mmRISC_1 is a RISC-V compliant CPU core with RV32IMAFC extensions supported ISA for building microcontrollers (MCU). You can even include this RISC-V core in your Questa Sim designs.

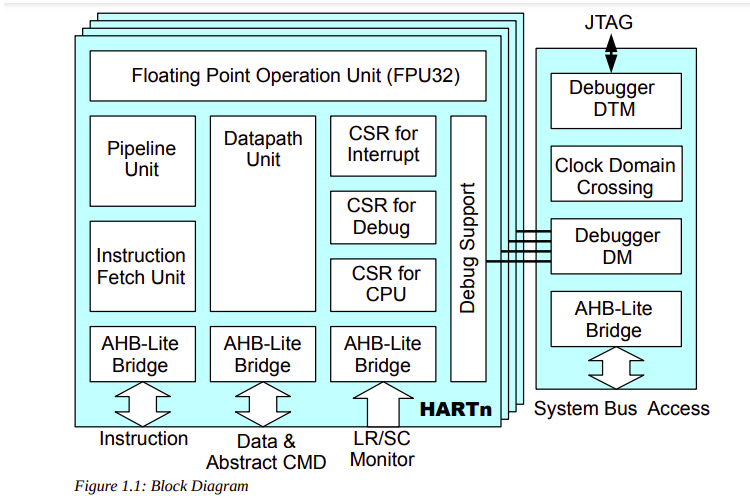

The mmRISC-1 contains multiple CPU Harts and a Debug Module with JTAG interface. Each Hart has instruction fetch bus, data access bus and monitor bus for LR/SC operation. The Debug Module has dedicated system bus access capability and controls each Hart (run / stop / step, etc.). The Debug Module can access resources in each Hart such as programer’s model registers (XRn, FRn), SCR (System Control Registers) and memory mapped devices through data access bus by debugger’s abstract commands. Each Hart consists of instruction fetch unit with pre-fetch buffer, pipeline unit with instruction decode, datapath unit for integer operations, CSR resources, debugger support and floating point operation unit. The monitor bus for LR/SC operation exists only when Atomic ISA is enabled. The floating point operation unit exists only when floating point ISA is enabled.

You can download the mmRISC-1 core here

Leave A Comment

You must be logged in to post a comment.